- 您现在的位置:买卖IC网 > Sheet目录308 > ADUM1300BRW (Analog Devices Inc)IC DIGITAL ISOLATOR 3CH 16-SOIC

Data Sheet

ADuM1300/ADuM1301

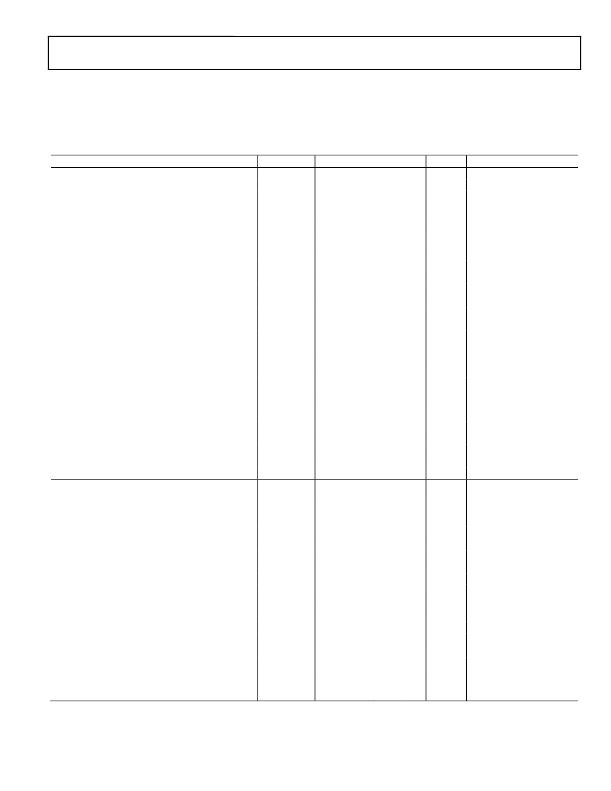

ELECTRICAL CHARACTERISTICS—3 V, 125°C OPERATION

All voltages are relative to their respective ground. 3.0 V ≤ V DD1 ≤ 3.6 V, 3.0 V ≤ V DD2 ≤ 3.6 V; all minimum/maximum specifications apply

over the entire recommended operation range, unless otherwise noted; all typical specifications are at T A = 25°C, V DD1 = V DD2 = 3.0 V.

These specifications apply to ADuM1300W and ADuM1301W automotive grade versions.

Table 5.

Parameter

Symbol

Min

Typ

Max

Unit

Test Conditions

DC SPECIFICATIONS

Input Supply Current per Channel, Quiescent

Output Supply Current per Channel, Quiescent

I DDI (Q)

I DDO (Q)

0.26

0.11

0.31

0.15

mA

mA

ADuM1300W, Total Supply Current, Three Channels 1

DC to 2 Mbps

V DD1 Supply Current

V DD2 Supply Current

I DD1 (Q)

I DD2 (Q)

0.9

0.4

1.7

0.7

mA

mA

DC to 1 MHz logic signal freq.

DC to 1 MHz logic signal freq.

10 Mbps (TRWZ Grade Only)

V DD1 Supply Current

V DD2 Supply Current

I DD1 (10)

I DD2 (10)

3.4

1.1

4.9

1.6

mA

mA

5 MHz logic signal freq.

5 MHz logic signal freq.

ADuM1301W, Total Supply Current, Three Channels 1

DC to 2 Mbps

V DD1 Supply Current

V DD2 Supply Current

I DD1 (Q)

I DD2 (Q)

0.7

0.6

1.4

0.9

mA

mA

DC to 1 MHz logic signal freq.

DC to 1 MHz logic signal freq.

10 Mbps (TRWZ Grade Only)

V DD1 Supply Current

V DD2 Supply Current

I DD1 (10)

I DD2 (10)

2.6

1.8

3.7

2.5

mA

mA

5 MHz logic signal freq.

5 MHz logic signal freq.

For All Models

Input Currents

I IA , I IB , I IC , I E1 , I E2

?10

+0.01 +10

μA

0 V ≤ V IA , V IB , V IC ≤ V DD1 or V DD2 ,

0 V ≤ V E1 , V E2 ≤ V DD1 or V DD2

Logic High Input Threshold

Logic Low Input Threshold

V IH , V EH

V IL , V EL

1.6

0.4

V

V

Logic High Output Voltages

V OAH , V OBH , V OCH

V DD1 , V DD2 ? 0.1 3.0

V DD1 , V DD2 ? 0.4 2.8

V

V

I Ox = ?20 μA, V Ix = V IxH

I Ox = ?4 mA, V Ix = V IxH

Logic Low Output Voltages

V OAL , V OBL , V OCL

0.0

0.04

0.2

0.1

0.1

0.4

V

V

V

I Ox = 20 μA, V Ix = V IxL

I Ox = 400 μA, V Ix = V IxL

I Ox = 4 mA, V Ix = V IxL

SWITCHING SPECIFICATIONS

ADuM130xWSRWZ

Minimum Pulse Width 2

Maximum Data Rate 3

PW

1

1000 ns

Mbps

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

Propagation Delay 4

Pulse Width Distortion, |t PLH ? t PHL | 4

Propagation Delay Skew 5

Channel-to-Channel Matching 6

t PHL , t PLH

PWD

t PSK

t PSKCD /t PSKOD

50

75

100 ns

40 ns

50 ns

50 ns

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

ADuM130xWTRWZ

Minimum Pulse Width 2

Maximum Data Rate 3

PW

10

100

ns

Mbps

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

Propagation Delay 4

Pulse Width Distortion, |t PLH ? t PHL | 4

t PHL , t PLH

PWD

20

34

45

3

ns

ns

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

Change vs. Temperature

5

ps/°C

C L = 15 pF, CMOS signal levels

Propagation Delay Skew 5

Channel-to-Channel Matching,

t PSK

t PSKCD

26

3

ns

ns

C L = 15 pF, CMOS signal levels

C L = 15 pF, CMOS signal levels

Codirectional Channels 6

Channel-to-Channel Matching,

t PSKOD

6

ns

C L = 15 pF, CMOS signal levels

Opposing-Directional Channels 6

Rev. I | Page 13 of 32

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

ADUM1310BRWZ

IC ISOLATOR DGTL 3CH UNI 16-SOIC

ADUM1400WTRWZ

IC ISOLATOR DIG 4CH 125C 16SOIC

ADUM1412BRWZ-RL

IC ISOLATOR DGTL QUAD 16-SOIC

ADUM1420BRWZ-RL

IC ISOLATOR DGTL 4CH 28SOIC

ADUM1510BRWZ-RL

IC DIGITAL ISOLATOR 16-SOIC

ADUM2210TRIZ

ISOLATOR DGTL 2CH 16SOIC

ADUM2250ARIZ-RL

ISOLATOR DL I2C HOT-SWAP 16SOIC

ADUM2400CRIZ

ISOLATOR DGTL 4CH 16SOIC

相关代理商/技术参数

ADUM1300BRW-RL

制造商:Analog Devices 功能描述:Digital Isolator Logic 3-CH 10Mbps 16-Pin SOIC W T/R 制造商:Rochester Electronics LLC 功能描述:

ADUM1300BRWZ

功能描述:IC DIGITAL ISOLATOR 3CH 16-SOIC RoHS:是 类别:隔离器 >> 数字隔离器 系列:iCoupler® 标准包装:66 系列:iCoupler® 输入 - 1 侧/2 侧:2/2 通道数:4 电源电压:3.3V,5V 电压 - 隔离:2500Vrms 数据速率:25Mbps 传输延迟:60ns 输出类型:逻辑 封装/外壳:20-SSOP(0.209",5.30mm 宽) 供应商设备封装:20-SSOP 包装:管件 工作温度:-40°C ~ 105°C

ADUM1300BRWZ-RL

功能描述:IC DIGITAL ISOL 3-CH 16SOIC TR RoHS:是 类别:隔离器 >> 数字隔离器 系列:iCoupler® 产品培训模块:IsoLoop® Isolator 标准包装:50 系列:IsoLoop® 输入 - 1 侧/2 侧:5/0 通道数:5 电源电压:3 V ~ 5.5 V 电压 - 隔离:2500Vrms 数据速率:110Mbps 传输延迟:12ns 输出类型:CMOS 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC N 包装:管件 工作温度:-40°C ~ 85°C 其它名称:390-1053-5

ADUM1300CRW

功能描述:IC DIGITAL ISOLATOR 3CH 16-SOIC RoHS:否 类别:隔离器 >> 数字隔离器 系列:iCoupler® 产品培训模块:IsoLoop® Isolator 标准包装:50 系列:IsoLoop® 输入 - 1 侧/2 侧:5/0 通道数:5 电源电压:3 V ~ 5.5 V 电压 - 隔离:2500Vrms 数据速率:110Mbps 传输延迟:12ns 输出类型:CMOS 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC N 包装:管件 工作温度:-40°C ~ 85°C 其它名称:390-1053-5

ADUM1300CRW-RL

功能描述:IC DIGITAL ISOL 3-CH 16SOIC TR RoHS:否 类别:隔离器 >> 数字隔离器 系列:iCoupler® 产品培训模块:IsoLoop® Isolator 标准包装:50 系列:IsoLoop® 输入 - 1 侧/2 侧:5/0 通道数:5 电源电压:3 V ~ 5.5 V 电压 - 隔离:2500Vrms 数据速率:110Mbps 传输延迟:12ns 输出类型:CMOS 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC N 包装:管件 工作温度:-40°C ~ 85°C 其它名称:390-1053-5

ADUM1300CRWZ

功能描述:IC DIGITAL ISOLATOR 3CH 16-SOIC RoHS:是 类别:隔离器 >> 数字隔离器 系列:iCoupler® 标准包装:66 系列:iCoupler® 输入 - 1 侧/2 侧:2/2 通道数:4 电源电压:3.3V,5V 电压 - 隔离:2500Vrms 数据速率:25Mbps 传输延迟:60ns 输出类型:逻辑 封装/外壳:20-SSOP(0.209",5.30mm 宽) 供应商设备封装:20-SSOP 包装:管件 工作温度:-40°C ~ 105°C

ADUM1300CRWZ-RL

功能描述:IC ISOLATOR DGTL 3CH 16SOIC RoHS:是 类别:隔离器 >> 数字隔离器 系列:iCoupler® 标准包装:66 系列:iCoupler® 输入 - 1 侧/2 侧:2/2 通道数:4 电源电压:3.3V,5V 电压 - 隔离:2500Vrms 数据速率:25Mbps 传输延迟:60ns 输出类型:逻辑 封装/外壳:20-SSOP(0.209",5.30mm 宽) 供应商设备封装:20-SSOP 包装:管件 工作温度:-40°C ~ 105°C

ADUM1300WSRWZ

功能描述:IC ISOLATOR DIG 3CH 125C 16SOIC RoHS:是 类别:隔离器 >> 数字隔离器 系列:iCoupler® 产品培训模块:IsoLoop® Isolator 标准包装:50 系列:IsoLoop® 输入 - 1 侧/2 侧:5/0 通道数:5 电源电压:3 V ~ 5.5 V 电压 - 隔离:2500Vrms 数据速率:110Mbps 传输延迟:12ns 输出类型:CMOS 封装/外壳:16-SOIC(0.154",3.90mm 宽) 供应商设备封装:16-SOIC N 包装:管件 工作温度:-40°C ~ 85°C 其它名称:390-1053-5